# Homework 4

(Due date: March 31<sup>st</sup> @ 5:30 pm)

Presentation and clarity are very important! Show your procedure!

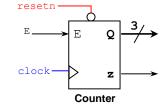

#### PROBLEM 1 (20 PTS)

- Design a counter using a Finite State Machine (FSM): Counter features:

- ✓ Count: 000, 010, 111, 011, 110, 100, 001, 101, 000, 010, 111, ...

- ✓ *resetn*: Asynchronous active-low input signal. It initializes the count to "000"

- ✓ Input *E*: Synchronous input that increases the count when it is set to `1'.

- ✓ output *z*: It becomes '1' when the count is 101.

- Provide the State Diagram (any representation), State Table, and the Excitation Table. Is this a Mealy or a Moore machine? Why? (10 pts)

- Provide the excitation equations (simplify your circuit using K-maps or the Quine-McCluskey algorithm) (5 pts)

- Sketch the circuit. (5 pts)

# PROBLEM 2 (15 PTS)

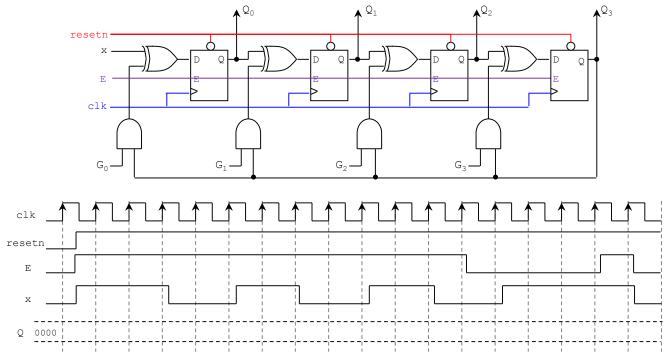

• Complete the timing diagram of the following circuit.  $G = G_3G_1G_2G_0 = 1001$ ,  $Q = Q_3Q_2Q_1Q_0$

# PROBLEM 3 (30 PTS)

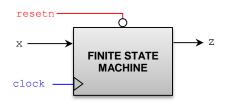

Sequence detector (with overlap): (10 pts) Draw the state diagram (any representation) of a circuit (with an input *x*) that detects the following sequence: 1010011. The detector must assert an output *z* when the sequence is detected.

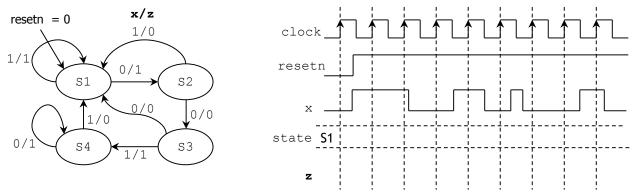

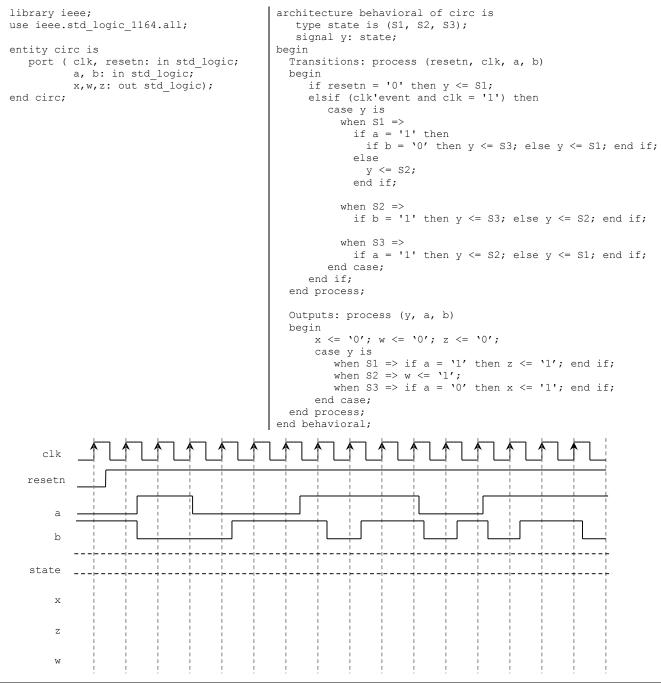

Complete the timing diagram of the following FSM. Is this a Mealy or a Moore machine? Why? (5 pts)

Provide the state diagram (in ASM form) and complete the timing diagram of the FSM whose VHDL description is listed below. (15 pts)

Instructor: Daniel Llamocca

#### PROBLEM 4 (20 PTS)

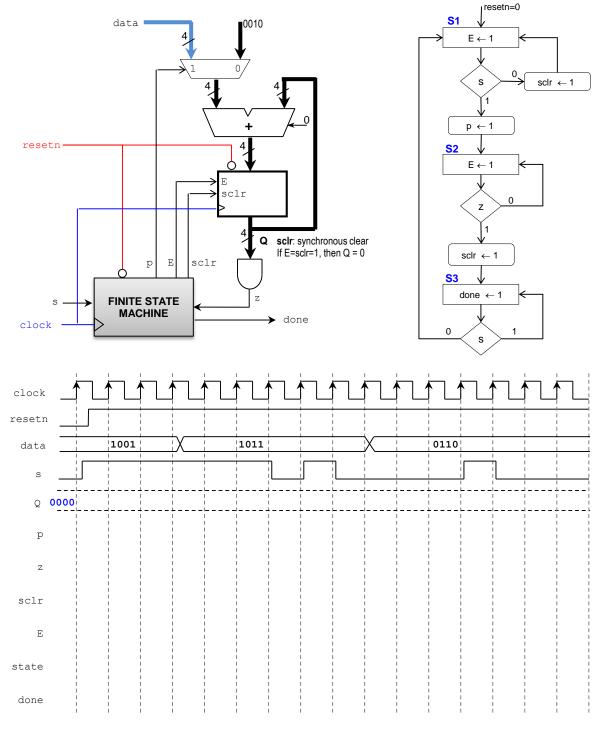

• Complete the timing diagram of the following digital circuit that includes an FSM (in ASM form) and a datapath circuit.

### PROBLEM 5 (15 PTS)

Attach a printout of your Project Status Report (no more than three pages, single-spaced, 2 columns). This report should contain the current status of the project. You <u>MUST</u> use the provided template (Final Project – Report Template.docx).